Rangkaian Pencacah (Counter)

Counter juga disebut pencacah atau penghitung yaitu rangkaian logika sekuensial yang digunakan untuk menghitung jumlah pulsa yang diberikan pada bagian masukan. Counter digunakan untuk berbagai operasi aritmatika, pembagi frekuensi, penghitung jarak (odometer), penghitung kecepatan (spedometer), yang pengembangannya digunakan luas dalam aplikasi perhitungan pada instrumen ilmiah, kontrol industri, komputer, perlengkapan komunikasi, dan sebagainya .

Counter tersusun atas sederetan flip-flop yang dimanipulasi sedemikian rupa dengan menggunakan peta Karnough sehingga pulsa yang masuk dapat dihitung sesuai rancangan. Dalam perancangannya counter dapat tersusun atas semua jenis flip-flop, tergantung karakteristik masing-masing flip-flop tersebut.

Dilihat dari arah cacahan, rangkaian pencacah dibedakan atas pencacah naik (Up Counter) dan pencacah turun (Down Counter). Pencacah naik melakukan cacahan dari kecil ke arah besar, kemudian kembali ke cacahan awal secara otomatis. Pada pencacah menurun, pencacahan dari besar ke arah kecil hingga cacahan terakhir kemudian kembali ke cacahan awal.

Tiga faktor yang harus diperhatikan untuk membangun pencacah naik atau turun yaitu (1) pada transisi mana Flip-flop tersebut aktif. Transisi pulsa dari positif ke negatif atau sebaliknya, (2) output Flip-flop yang diumpankan ke Flip-flop berikutnya diambilkan dari mana. Dari output Q atau Q, (3) indikator hasil cacahan dinyatakan sebagai output yang mana. Output Q atau Q. ketiga faktor tersebut di atas dapat dinyatakan dalam persamaan EX-OR.

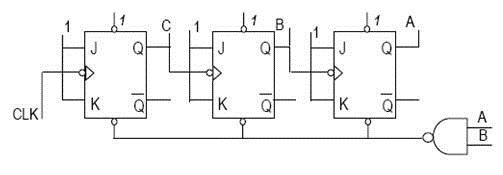

Secara global counter terbagi atas 2 jenis, yaitu: Syncronus Counter dan Asyncronous counter. Perbedaan kedua jenis counter ini adalah pada pemicuannya. Pada Syncronous counter pemicuan flip-flop dilakukan serentak (dipicu oleh satu sumber clock) susunan flip-flopnya paralel. Sedangkan pada Asyncronous counter, minimal ada salah satu flip-flop yang clock-nya dipicu oleh keluaran flip-flop lain atau dari sumber clock lain, dan susunan flip-flopnya seri. Dengan memanipulasi koneksi flip-flop berdasarkan peta karnough atau timing diagram dapat dihasilkan counter acak, shift counter (counter sebagai fungsi register) atau juga up-down counter.

1). Synchronous Counter

Syncronous counter memiliki pemicuan dari sumber clock yang sama dan susunan Flip-Flop adalah parallel. Dalam Syncronous counter ini sendiri terdapat perbedaan penempatan atau manipulasai gerbang dasarnya yang menyebabkan perbedaan waktu tunda yang disebut carry propagation delay

Penerapan counter dalam aplikasinya adalah berupa chip IC baik IC TTL, maupun CMOS, antara lain adalah: (TTL) 7490, 7493, 74190, 74191, 74192, 74193, (CMOS) 4017,4029,4042,dan lain-lain.

Pada Counter Sinkron, sumber clock diberikan pada masing-masing input Clock dari Flip-flop penyusunnya, sehingga apabila ada perubahan pulsa dari sumber, maka perubahan tersebut akan men-trigger seluruh Flip-flop secara bersama-sama.

Tabel Kebenaran untuk Up Counter dan Down Counter Sinkron 3 bit :

Counter Asinkron Mod-N

Counter Mod-N adalah Counter yang tidak 2n. Misalkan Counter Mod-6, menghitung : 0, 1, 2, 3, 4, 5. Sehingga Up Counter Mod-N akan menghitung 0 s/d N-1, sedangkan Down Counter MOD-N akan menghitung dari bilangan tertinggi sebanyak N kali ke bawah. Misalkan Down Counter MOD-9, akan menghitung : 15, 14, 13, 12, 11, 10, 9, 8, 7, 15, 14, 13,..

Gambar rangkaian Up Counter Asinkron Mod-6

Sebuah Up Counter Asinkron Mod-6, akan menghitung : 0,1,2,3,4,5,0,1,2,… Maka nilai yang tidak pernah dikeluarkan adalah 6. Jika hitungan menginjak ke-6, maka counter akan reset kembali ke 0. Untuk itu masing-masing Flip-flop perlu di-reset ke nilai ”0” dengan memanfaatkan input-input Asinkron-nya (

Sumber : https://adityarizki.net/tutorial-teknik-digital-rangkaian-pencacah-counter/

Dibawah ini 2 video penerapan rangkaian counter

No comments:

Post a Comment